### Evaluates: MAX98357A/MAX98357B (TQFN)

#### **General Description**

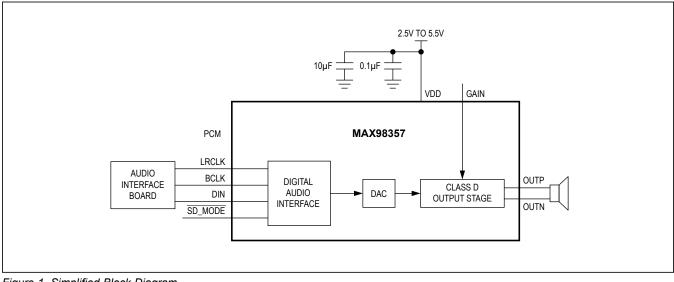

The MAX98357 development board (DEV board) is a fully assembled and tested PCB that evaluates the MAX98357 I<sup>2</sup>S digital input Class D power amplifier. The DEV board operates from a single 2.5V to 5.5V DC power supply and is capable of delivering 3.2W into a 4 $\Omega$  load. The device outputs can be connected directly to a speaker load for filterless applications. However, a filter can be added to ease evaluation. The MAX98357A accepts standard I<sup>2</sup>S data and the MAX98357B accepts left-justified digital audio data. Both versions also support 8-channel TDM audio data.

The MAX98357 evaluation system (EV system) includes the MAX98357 DEV board and Maxim Integrated's audio interface board (AUDINT001 board).

The AUDINT001 board provides an easy-to-use USB audio-to-I<sup>2</sup>S converter. This allows for any computer to become a digital audio source, which can be used to evaluate the devices. The AUDINT001 board can also be used to power the MAX98357. This allows for a complete evaluation from a single USB connection.

#### **Features**

- 2.5V to 5.5V Single-Supply Operation

- Only a Single External Component (VDD Capacitor) Required in Many Applications

- I2S, Left-Justified, or TDM Input

- Five Selectable Gains (3db, 6dB, 9dB, 12dB, and 15dB)

- Audio Channel Select (Left, Right, and Mono Mix)

- Filterless Operation

- Optional Class D Output Filters for Ease of Evaluation

- Proven PCB Layout

- Fully Assembled and Tested

Ordering Information appears at end of data sheet.

Figure 1. Simplified Block Diagram

19-6843; Rev 1; 4/14

#### **Quick Start**

#### **Recommended Equipment**

- MAX98357 EV system

- 2.5V to 5.5V, 2A DC power supply

- USB audio source (from computer through an audio media player such as iTunes<sup>®</sup> or Windows Media<sup>®</sup> player)

- 4Ω or 8Ω speaker

#### Procedure

The EV system is fully assembled and tested. Follow the steps below to verify board operation. Caution: Do not turn on the power supply until all connections are completed.

1) On the DEV board verify that headers and switches are configured as follows:

JU2: Pins 1-3 (selects left channel)

- JU4: Pins 1-2 (power routed from the AUDINT001 board)

- JU5: Pins 1-5 (12dB gain)

JU6: Pins 2-3 (power routed from external supply)

SW1: Position 1-2 (part is on)

- 2) Set the power-supply output to 5V. Disable the power supply.

- Connect the power-supply ground terminal to GND and the power-supply positive terminal to VIN on the DEV board.

- 4) With the audio source disabled, connect the USB audio source to the USB AUDIO port (USB2) on the AUDINT001 board.

- 5) Connect the AUDINT001 board to J1 on the DEV board.

- 6) Connect the speaker across the OUTP and OUTN test points.

- 7) Enable the power-supply output.

- 8) Enable the audio source.

- 9) Verify that the speakers are playing the audio source signal.

## Evaluates: MAX98357A/MAX98357B (TQFN)

#### **Detailed Description of Hardware**

The MAX98357 EV system is designed to allow a thorough evaluation of the MAX98357 I<sup>2</sup>S digital input Class D power amplifier. The DEV board can be used by itself as a stand-alone evaluation board and driven directly by audio test equipment. The DEV board can also be used in conjunction with the AUDINT001 board, which allows for any computer to become an I<sup>2</sup>S digital audio source.

The AUDINT001 board has DC regulators that can be used to power the device. This allows for quick evaluation from a single USB connection. Note that powering the device from the AUDINT001 board does not allow for high-power evaluation as the input current is limited and evaluation with a speaker is not recommended. Jumpers JU4 and JU6 are used to power the device from the AUDINT001 board or external supplies connected to test points VIN and VDDIO on the DEV board.

The DEV board operates from a single 2.5V to 5.5V DC power supply and is capable of delivering 3.2W into a 4 $\Omega$  load and 1.75W into an 8 $\Omega$  load. The device outputs can be connected directly to a speaker for filterless applications. However, a filter can be added to ease evaluation. The LRC components needed for evaluation of a filtered output are included with the EV kit. The MAX98357A accepts standard I<sup>2</sup>S data and the MAX98357B accepts left-justified digital audio data. Both versions also support 8-channel TDM audio data.

#### **Filterless Output**

The DEV board filterless outputs (OUTP, OUTN) can be connected directly to a speaker load without any filtering. Use the OUTP and OUTN test points to connect the speaker directly to the device output.

#### **Filtered Output**

Audio analyzers typically cannot accept the Class D amplifier's pulse-width modulated (PWM) signals at their inputs. Therefore, the DEV board features optional low-pass filters at the outputs to ease evaluation. As shipped, the DEV board's lowpass filter LRC components are unpopulated and L1, L2 are shorted on the PCB.

To use the filtered output posts (FOUTP, FOUTN), remove the shorts on L1 and L2 and install components L1, L2, C3–C9, and R5, R6. (L1 and L2 are provided separately with the DEV board. Components C3–C12 and R5 and R6 are not included.) Use the output posts to connect the

iTunes is a registered trademark of Apple Inc.

Windows Media is registered trademark and registered service mark of Microsoft Corporation.

www.maximintegrated.com

filtered outputs to the audio analyzer. The default lowpass filters at the DEV board output are optimized for a  $4\Omega$  speaker.

#### **Jumper Selection**

#### Selectable Gain (GAIN\_SLOT)

The DEV board features a 5-pin jumper (JU5) to control the device's five programmable gain settings. In TDM mode, the gain is fixed at 12dB and the gain pin is repurposed for slot selection. See Table 1 for gain-control configuration.

#### SD\_MODE Input

The DEV board features a 4-pin jumper (JU2) to control both the audio channel that is sent to the amplifier output, along with shutdown mode. JU2 is used to select the stereo input data between the left channel, right channel, and the sum of the left/right channels. JU5 must be set to pins 1-2 and a voltage applied to the +3.3V PCB pad for proper operation. See Table 2 for shunt positions.

## Table 1. JU5 Jumper Selection (GAIN SLOT)

| SHUNT<br>POSITION GAIN PIN |                                                                                                  | MAXIMUM<br>GAIN (dB) |

|----------------------------|--------------------------------------------------------------------------------------------------|----------------------|

| 1-2                        | 1-2         Connected to VDD through<br>100kΩ resistor R1           1-3         Connected to VDD |                      |

| 1-3                        |                                                                                                  |                      |

| 1-4                        | Connected to GND through $100k\Omega$ resistor R2                                                | 15                   |

| 1-5*                       | Connected to GND                                                                                 | 12                   |

| Not installed              | Unconnected                                                                                      | 9                    |

\*Default position.

## Table 2. JU2 Jumper Selection (SD\_MODE)

| SHUNT<br>POSITION | SD_MODE PIN                                           | AUDIO<br>CHANNEL             |  |

|-------------------|-------------------------------------------------------|------------------------------|--|

| 1-2               | 1-2 Connected to VDDIO<br>through R3 (small resistor) |                              |  |

| 1-3*              | Connected to VDDIO through a 2kΩ resistor             | Left                         |  |

| 1-4               | Connected to VDDIO<br>through R4 (large resistor)     | Mono mix<br>(left + right)/2 |  |

\*Default position.

#### **TDM Mode**

In TDM mode, the device has a fixed gain of 12dB and the gain pin becomes repurposed for slot selection. The device accepts 8-channel TDM data. The data can be either 16 bits or 32 bits wide. The GAIN\_SLOT pin and SD\_MODE are used to select which of 8 channels of TDM data the part responds to, as shown in Table 3.

#### **Shutdown Mode**

The device features a low-power shutdown mode that is activated by setting jumper SW1 to pins 2-3. To exit shutdown mode, set SW1 to pins 1-2 and select the desired stereo input channel using jumper JU2. See Table 4 for switch positions.

#### Table 3. TDM Mode Channel Selection

| JU2           | JU5   | CHANNEL | BITS     |  |

|---------------|-------|---------|----------|--|

| Connected low | Х     | OFF     | N/A      |  |

| (1-3)         | (1-5) | 0       | 16 or 32 |  |

| (1-3)         | (1-3) | 1       | 16 or 32 |  |

| (1-3)         | Open  | 2       | 16 or 32 |  |

| (1-3)         | (1-2) | 3       | 16 or 32 |  |

| (1-3)         | (1-4) | 4       | 16 or 32 |  |

| (1-4)         | (1-5) | 5       | 16 or 32 |  |

| (1-4)         | Open  | 6       | 16 or 32 |  |

| (1-4)         | (1-3) | 7       | 16 or 32 |  |

#### Table 4. SW1 Switch Configuration

| SWITCH<br>POSITION | VDDIO<br>VOLTAGE                              | DEVICE<br>OPERATION                                       |

|--------------------|-----------------------------------------------|-----------------------------------------------------------|

| 1-2*               | VDDIO determined<br>by JU4 jumper<br>position | Normal<br>(input channel selected<br>through JU2 setting) |

| 2-3                | Connected to GND                              | Shutdown                                                  |

\*Default position.

#### External/Internal VDDIO (+1.8V to +3.3V)

On the DEV board, a logic voltage from a control interface is needed for proper selection of the stereo input channel through  $\overline{SD}_{MODE}$ . This voltage can be applied externally at the VDDIO test point or it can be provided from circuitry on the AUDINT001 board. See Table 5 for JU4 jumper selection.

Logic voltages other than +3.3V can be used. If you want to use other logic voltages, resistors R3 and R4 must be adjusted. Refer to the  $\overline{SD\_MODE}$  and Shutdown Operation section in the MAX98357 IC data sheet for more information.

#### VDD Input Supply (+2.5V to +5.5V)

The device can accept an input supply from +2.5V to +5.5V. This voltage can be applied externally at the VDD and GND PCB pads, or it can be provided from the AUDINT001 board. See Table 6 for JU6 jumper selection.

#### Audio Interface Board (AUDINT001 Board)

The AUDINT001 board provides USB-to-I<sup>2</sup>S data conversion, as well as DC regulators that can be used to power the devices. The USB-to-I<sup>2</sup>S converter on the AUDINT001

### Evaluates: MAX98357A/MAX98357B (TQFN)

board allows for any computer to become an I<sup>2</sup>S digital audio source. On the AUDINT001 board, set SW1 to "demo" and set the I<sup>2</sup>S switch to connected to source audio by USB. This allows for a quick evaluation from a single USB connection. Using the AUDINT001 board as a power supply for high-power evaluation is not recommended as the input current is limited. For high-power evaluation, use an external supply connected to VIN.

#### Driving I<sup>2</sup>S Directly

To drive I<sup>2</sup>S directly, apply signals at the BCLK, LRCLK, and SDIN test points, or on the J3 header, or between J3 pins 1-2 at the appropriate locations (signal and ground are labeled on the board).

#### Evaluating the MAX98357B

The MAX98357 DEV board comes with a MAX98357A populated on the board, but can be used to evaluate the MAX98357B. To evaluate the MAX98357B, carefully remove the MAX98357A (U1) device from the board and replace with MAX98357BETE+. No other component changes are required.

#### Table 5. JU4 Jumper Selection (VDDIO)

| SHUNT<br>POSITION | LOGIC VOLTAGE (VDDIO)                                                |

|-------------------|----------------------------------------------------------------------|

| 1-2*              | 3.3V supplied by the AUDINT001 board<br>connected to J1 header.      |

| 2-3               | User-supplied external power supply applied at the VDDIO test point. |

\*Default position.

#### Table 6. JU3 Jumper Selection (VDD)

| SHUNT<br>POSITION |                                                                   |  |

|-------------------|-------------------------------------------------------------------|--|

| 1-2*              | VDD supplied from the AUDINT001 board connected to the J1 header. |  |

| 2-3               | User-supplied external power supply applied at the VIN PCB pad.   |  |

\*Default position.

## Evaluates: MAX98357A/MAX98357B (TQFN)

### **Component List**

| DESIGNATION                    | QTY | DESCRIPTION                                                                                                        |

|--------------------------------|-----|--------------------------------------------------------------------------------------------------------------------|

| BCLK, DIN,<br>LRCLK            | 3   | Orange multipurpose test points                                                                                    |

| C1                             | 1   | 10µF ±10%, 6.3V X5R<br>ceramic capacitor (0603)<br>Murata GRM188R60J106K                                           |

| C2                             | 1   | 0.1µF ±10%, 16V X7R<br>ceramic capacitor (0402)<br>Murata GRM155R71C104K                                           |

| C3–C12                         | 0   | Not installed, ceramic capacitors (0402)                                                                           |

| C11                            | 1   | 22pF ±5%, 50V C0G ceramic<br>capacitor (0402)<br>Murata GRM1555C1H220J                                             |

| FB1, FB2                       | 2   | 0Ω ±5% resistors (0603)                                                                                            |

| FOUTN, FOUTP,<br>GND, VIN      | 4   | Binding posts                                                                                                      |

| FOUTN, FOUTP,<br>GND (x2), VDD | 5   | 20G plated solid copper bus<br>wire, 0.25in U-shaped wire<br>loop                                                  |

| GND (x4), OUTN                 | 5   | Black multipurpose test points (63 mil drill size)                                                                 |

| J1                             | 1   | 26-pin (2 x 13) dual-row right-<br>angle header, 0.1in centers                                                     |

| J3                             | 1   | 6-pin header                                                                                                       |

| JU2                            | 1   | 4-pin header, 0.1 in centers                                                                                       |

| JU4, JU6                       | 2   | 3-pin headers, 0.1 in centers                                                                                      |

| JU5                            | 1   | 5-pin header, 0.1 in centers                                                                                       |

| L1, L2                         | 0   | Not installed, 22µH inductors<br>(6.2mm x 6.3mm)—short<br>(PC trace)<br>TOKO D63CB series part<br>TOKO A916CY-220M |

| DESIGNATION    | QTY   | DESCRIPTION                                                                        |

|----------------|-------|------------------------------------------------------------------------------------|

| OUTP           |       | White multipurpose test point (63 mil drill size)                                  |

| R1, R2         | 2     | $100k\Omega \pm 5\%$ resistors (0603)                                              |

| R3             | 1     | 226kΩ ±1% resistor (0603)                                                          |

| R4             | 1     | 634kΩ ±1% resistor (0603)                                                          |

| R5, R6         | 0     | Not installed, resistors (0402)                                                    |

| R7–R9          | 3     | $0\Omega \pm 5\%$ resistors (0603)                                                 |

| SW1            | 1     | SPDT jumper switch, 0.1in centers                                                  |

| U1             | 1     | I <sup>2</sup> S input Class D audio<br>amplifier (16 TQFN)<br>Maxim MAX98357AETE+ |

| VDDIO 1        |       | Red multipurpose test point (63 mil drill size)                                    |

| _              | 4     | Shunts                                                                             |

| _              | 1     | PCB: MAX98357 TQFN<br>EVKIT DEVELOPMENT<br>BOARD                                   |

| OPTIONAL COMPO | NENTS |                                                                                    |

| C3–C9          | 7     | 0.22µF ±10%, 6.3V X5R<br>ceramic capacitors (0402)<br>TDK C1005X5R0J224K           |

| C10–C12 3      |       | 18pF ±5%, 50V C0G ceramic capacitors (0402)                                        |

| L1, L2         | 2     | 22µH, 1A inductors<br>(6.2mm x 6.3mm)<br>ТОКО А916СҮ-220М                          |

| R5, R6         | 2     | 22Ω ±5% resistors (0402)                                                           |

| R7–R9          | 3     | 51Ω ±5% resistors (0402)                                                           |

### **Component Suppliers**

| SUPPLIER           | PHONE        | WEBSITE                |

|--------------------|--------------|------------------------|

| Murata Americas    | 770-436-1300 | www.murataamericas.com |

| TDK Corp.          | 847-803-6100 | www.component.tdk.com  |

| TOKO America, Inc. | 847-297-0070 | www.tokoam.com         |

Note: Indicate that you are using the MAX98357A/MAX98357B TQFN when contacting these component suppliers.

Evaluates: MAX98357A/MAX98357B (TQFN)

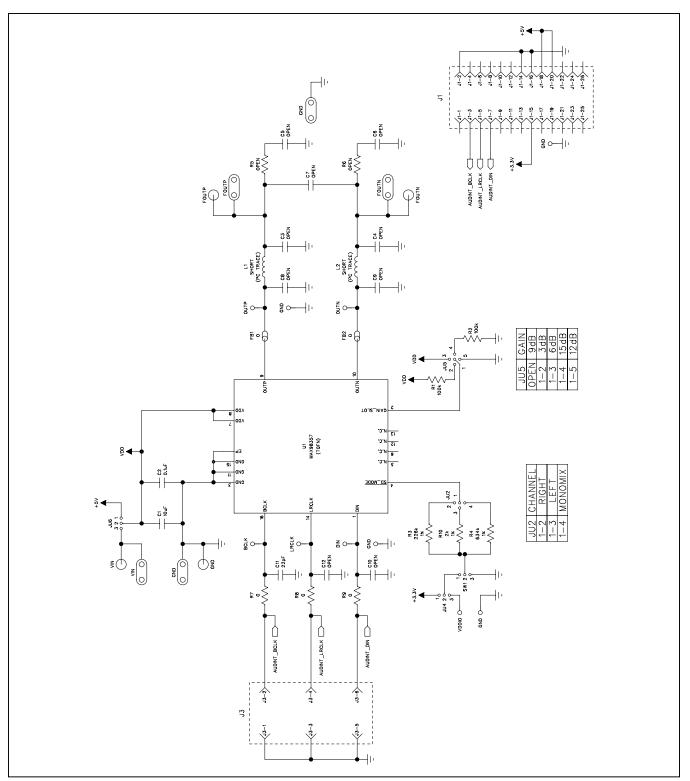

Figure 2. MAX98357 DEV Board Schematic

### Evaluates: MAX98357A/MAX98357B (TQFN)

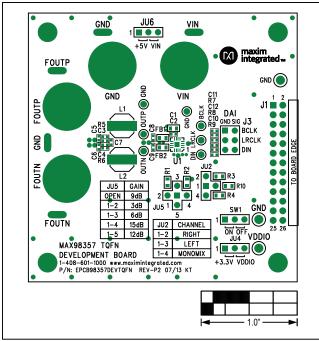

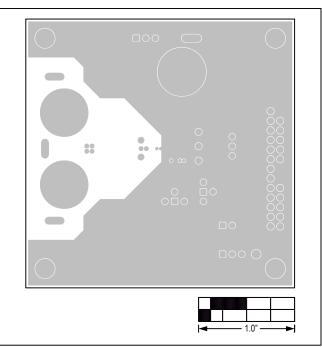

Figure 3. MAX98357 DEV Board Silkscreen—Top

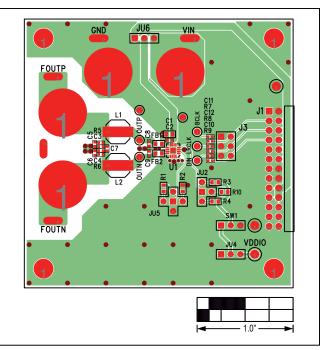

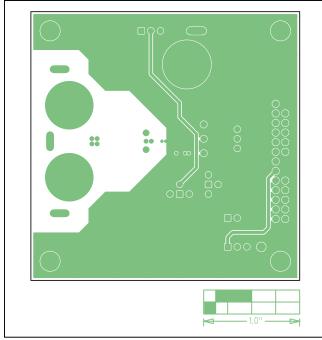

Figure 4. MAX98357 DEV Board PCB Layout—Component Side

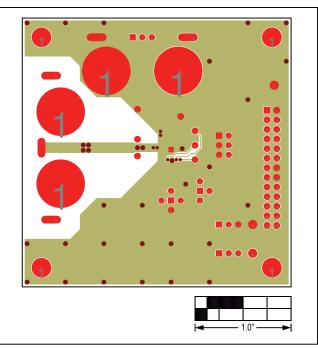

Figure 5. MAX98357 DEV Board PCB Layout—Layer 2

www.maximintegrated.com

### Evaluates: MAX98357A/MAX98357B (TQFN)

Figure 6. MAX98357 DEV Board PCB Layout—Layer 3

Figure 7. MAX98357 DEV Board PCB Layout—Solder Side

### **Ordering Information**

| PART               | ТҮРЕ                                          |

|--------------------|-----------------------------------------------|

| MAX98357DEV#TQFN   | Development Board<br>(DEV Board only)         |

| MAX98357EVSYS#TQFN | Evaluation System<br>(DEV + AUDINT001 Boards) |

#Denotes RoHS compliant.

## Evaluates: MAX98357A/MAX98357B (TQFN)

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                             | PAGES<br>CHANGED |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 11/13            | Initial release                                                                                                                         | —                |

| 1                  | 4/14             | Added <i>Evaluating the MAX98357B</i> section, moved VDDIO to new pin on J1, added a 22pF capacitor to C11, and updated Figures 2 and 6 | 4–6, 8           |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc. © 2014 Maxim Integrated Products, Inc. 9